Thus, J must be a 1, but K can be at either level for this transition to occur.ġ to 0 transition: The PRESENT state is 1 and is to change to a 0, which can happen when either J = 0 and K = 1 or J = K = 1. Recall that “ x” means the don’t-care condition.Ġ to 1 transition: The PRESENT state is 0 and is to change to a 1, which can happen when either J = 1 and K = 0 (set condition) or J = K = 1 (toggle condition). The table indicates this with a “0” under J and an “ x” under K. Thus, J must be at 0, but K can be at either level. From our understanding of how a J-K flip-flop works, this can happen when either J = K = 0 (no-change condition) or J = 0 and K = 1 (clear condition). The operation of the J-K flip-flop using the Transition table is explained below:Ġ to 0 transition: The FF PRESENT state is at 0 and is to remain at 0 when a clock pulse is applied. Table 1: J -K Excitation Table OR J -K Transition Table When J and K are both HIGH, the flip-flop changes state. When both J and K are LOW, the output does not change from its prior state. When J is LOW and K is HIGH, the Q output goes LOW on the triggering edge of the clock pulse, and the flip-flop is RESET. When J is HIGH and K is LOW, the Q output goes HIGH on the triggering edge of the clock pulse, and the flip-flop is SET. The J and K inputs of the J-K flip-flop are synchronous inputs because data on these inputs are transferred to the flip-flop’s output only on the triggering edge of the clock pulse. The basic operation of a positive edge-triggered J-K flip-flop is illustrated in Figure1.2 Operation of the Positive-edge triggered J-K flip-flop

This OFF-ON action is like a toggle switch and is called toggling. When both data inputs J and K are at 1, repeated clock pulses cause the output to turn off-on-off-on-off-on, and so forth. Line 4 illustrates the useful toggle position of the J-K flip-flop. Lines 2 and 3 of the truth table show the reset and set conditions for the Q output.

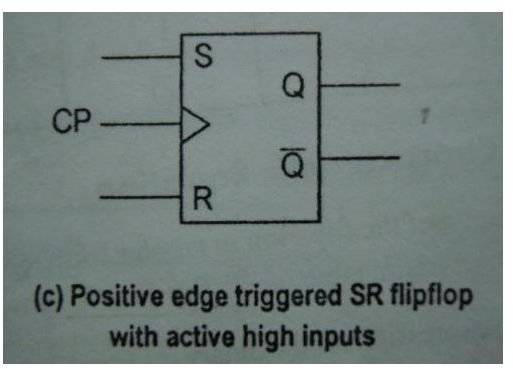

The outputs “hold” the last data present. In the hold mode, the data inputs have no effect on the outputs. When the J and K inputs are both 0, the flip-flop is in the hold mode. Figure 1.1 Positive-edge triggered J-K flip-flop (a) Logic symbol (b) Truth table

0 kommentar(er)

0 kommentar(er)